原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

1. 软件环境

软件开发环境基于Vivado 2020.1

2. 硬件环境

| 开发板型号 | 芯片型号 |

| AXU2CGA | xczu2cg-sfvc784-1-e |

| AXU2CGB | xczu2cg-sfvc784-1-e |

3. 批处理下载QSPI Flash

所有的工程目录下都有个bootimage文件夹,存放了对应的BOOT.bin文件,可将此文件拷贝到Vitis_image_download文件夹,覆盖原有的BOOT.bin。也可以把BOOT.bin放到SD卡启动验证功能

vitis_image_download文件夹在course_s2目录下面,进入文件夹,右键点击program_qspi.bat,打开编辑

将program_flash路径改成自己的软件安装路径,保存并关闭。

双击program_qspi.bat,即可下载BOOT.BIN到QSPI FLASH,建议用JTAG模式下载。

也可以采用SD卡启动方法,把BOOT.bin文件拷贝到SD内启动。

4. 批处理建立Vitis工程

由于Vitis工程编译后占用空间较大,因此为了节省大家宝贵的时间,我们提供了Vitis工程的批处理tcl脚本,在每个工程下都有个vitis文件夹,里面包含硬件描述文件xx.xsa,以及自动创建工程的脚本

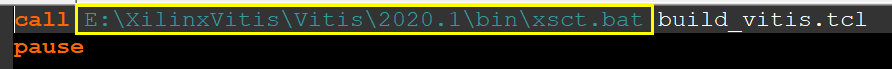

大家需要做的是编辑auto_create_vitis文件夹中的build_vitis.bat文件

将黄色框中的xsct.bat路径换成自己安装的路径,路径为xx\Vitis\2020.1\bin\xsct.bat

保存之后,再双击build_vitis.bat就可以创建工程了

编译结束,按任意键退出

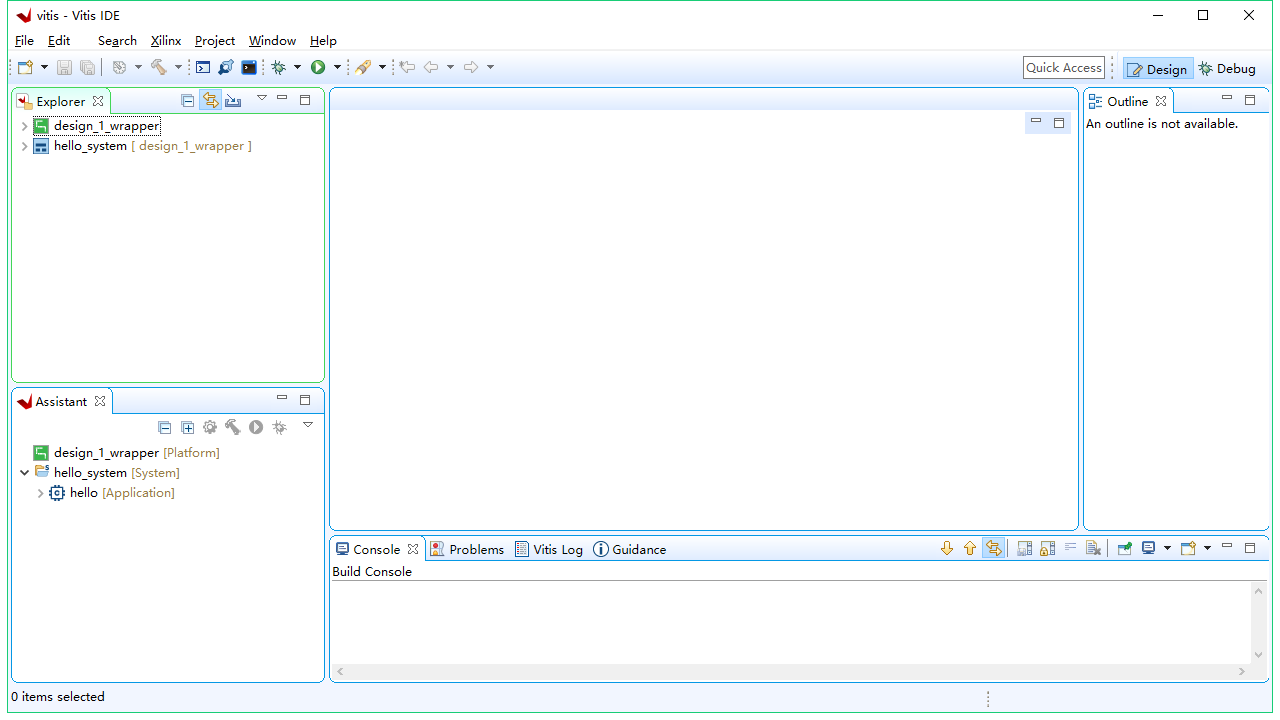

打开Vitis软件,选择工程路径,Launch

打开后,关闭Welcom界面

工程即可使用