原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处(http://www.alinx.com)。

适用于板卡型号:

PGL22G/PGL12G

1. 实验简介

HDMI做为视频输出输入接口已经广泛使用很长时间,主要通过TMDS差分编码传输。本实验通过在HDMI屏幕上显示彩条,来练习视频的时序和视频颜色的表示,为后面视频处理实验做个基础。

2. 实验原理

2.1 硬件介绍

开发板使用4对TMDS差分显示, 其中一对是时钟,其他三对是数据。

HDMI采用和DVI相同的传输原理——TMDS(Transition Minimized Differential signal),最小化传输差分信号。

TMDS传输系统分为分为两个部分:发送端和接收端。TMDS发送端收到HDMI接口传来的表示RGB信号的24位并行数据(TMDS对每个像素的RGB三原色分别按8bit编码,即R信号有8位,G信号有8位,B信号有8位),然后对这些数据进行编码和并/串转换,再将表示3个RGB信号的数据分别分配到独立的传输通道发送出去。接收端接收来自发送端的串行信号,对其进行解码和串/并转换,然后发送到显示器的控制端。与此同时也接收时钟信号,以实现同步。

TMDS的原理

每一个TMDS链路都包括3个传输RGB信号的数据通道和1个传输时钟信号的通道。每一个数据通道都通过编码算法,将8位的视、音频数据转换成最小化传输、直流平衡的10位数据。这使得数据的传输和恢复更加可靠。最小化传输差分信号是通过异或及异或非等逻辑算法将原始8位信号数据转换成10位,前8为数据由原始信号经运算后获得,第9位指示运算的方式,第10位用来对应直流平衡。

一般来说,HDMI传输的编码格式中要包含视频数据、控制数据和数据包(数据包中包含音频数据和附加信息数据,例如纠错码等)。TMDS每个通道在传输时要包含一个2bit的控制数据、8bit的视频数据或者4bit的数据包即可。在HDMI信息传输过程中,可以分为三个阶段:视频数据传输周期、控制数据传输周期和数据岛传输周期,分别对应上述的三种数据类型。

下面介绍TMDS中采用的技术:

1.传输最小化

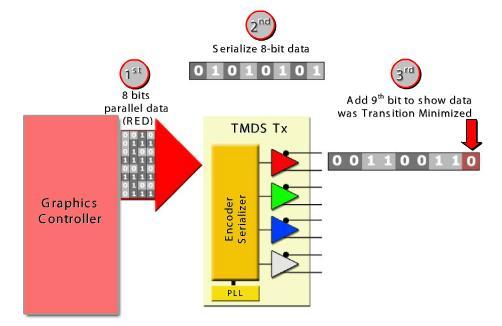

8位数据经过编码和直流平衡得到10位最小化数据,这仿佛增加了冗余位,对传输链路的带宽要求更高,但事实上,通过这种算法得到的10位数据在更长的同轴电缆中传输的可靠性增强了。下图是一个例子,说明对一个8位的并行RED数据编码、并/串转换。

第一步:将8位并行RED数据发送到TMDS发送端。

第二步:并/串转换.

第三步:进行最小化传输处理,加上第9位,即编码过程。第9位数据称为编码位。

2.直流平衡

直流平衡(DC-balanced)就是指在编码过程中保证信道中直流偏移为零。方法是在原来的9位数据的后面加上第10位数据,这样,传输的数据趋于直流平衡,使信号对传输线的电磁干扰减少,提高信号传输的可靠性。

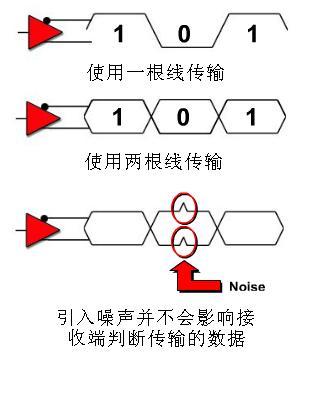

3.差分信号

TMDS差分传动技术是一种利用2个引脚间电压差来传送信号的技术。传输数据的数值(“0”或者“1”)由两脚间电压正负极性和大小决定。即,采用2根线来传输信号,一根线上传输原来的信号,另一根线上传输与原来信号相反的信号。这样接收端就可以通过让一根线上的信号减去另一根线上的信号的方式来屏蔽电磁干扰,从而得到正确的信号。

如下图所示:

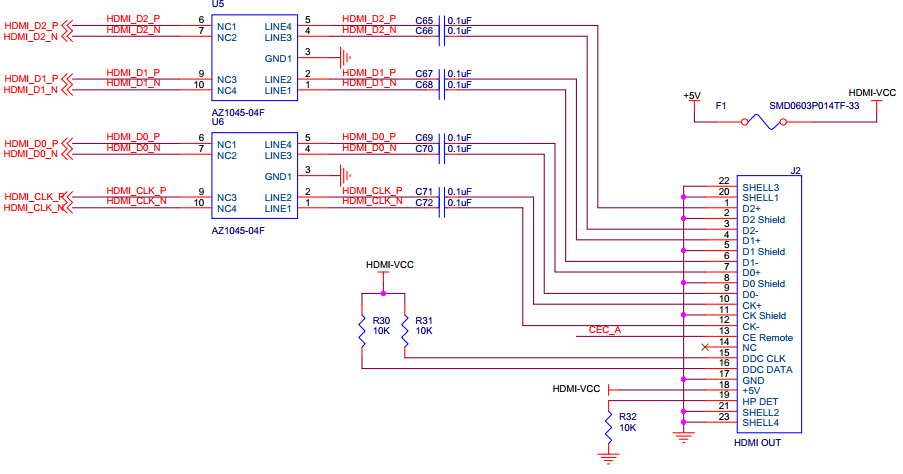

另外,还有一个显示数据通道(DDC),是用于读取表示接收端显示器的清晰度等显示能力的扩展显示标识数据(EDID)的信号线。搭载HDCP(High-bandwidth Digital Content Protection,高带宽数字内容保护技术)的发送、接收设备之间也利用DDC线进行密码键的认证。

HDMI输出部分电路

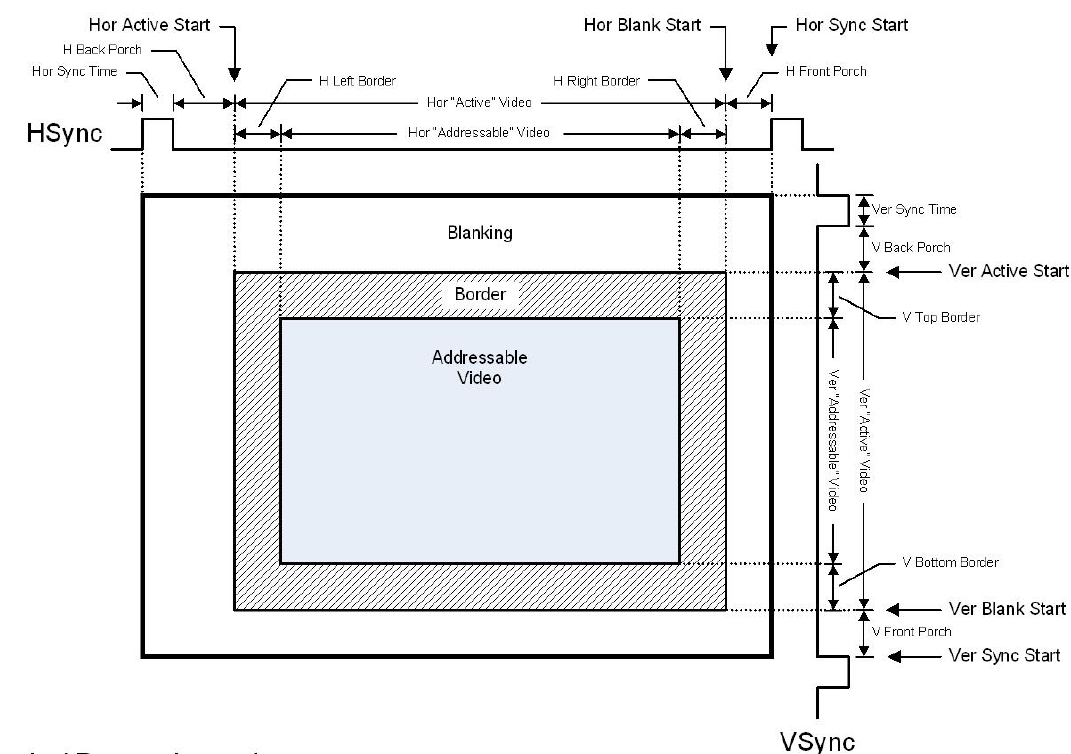

2.2 视频时序标准

HDMI显示器扫描方式从屏幕左上角一点开始,从左向右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

完成一行扫描的时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描的时间称为垂直扫描时间,其倒数称为场频率,即刷新一屏的频率,常见的有60Hz,75Hz等等。标准的显示的场频60Hz。

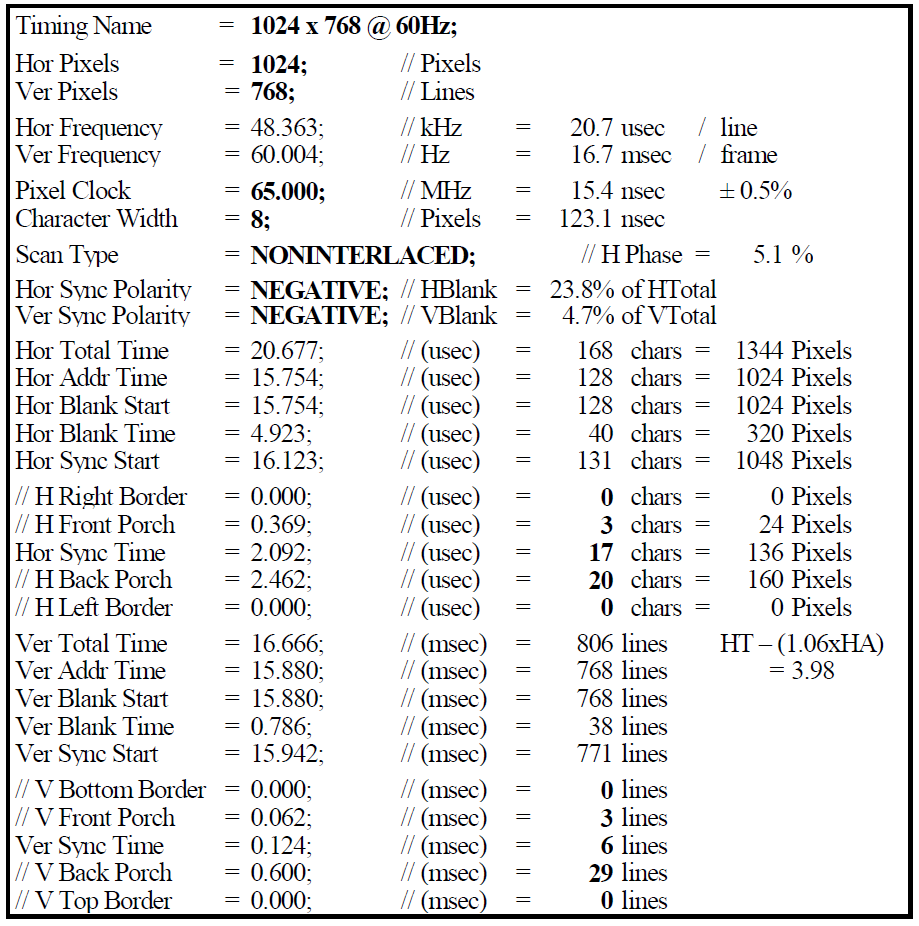

时钟频率:以1024x768@59.94Hz(60Hz)为例,每场对应806个行周期,其中768为显示行。每显示行包括1344点时钟,其中1024点为有效显示区。由此可知:需要点时钟频率:806*1344*60约65MHz。

视频时序

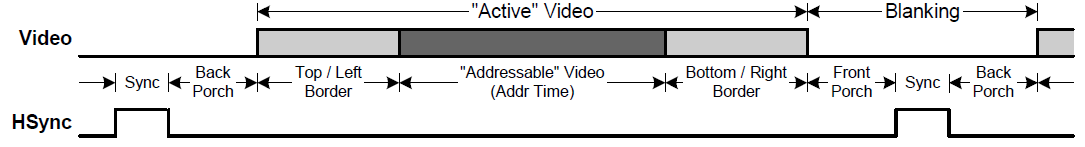

VGA扫描,基本元素是行扫描,多行组成一帧,下图显示一行的时序,其中“Active”Video是一行视频的有效像素,大部分分辨率时钟中Top/Left Border 和 Bottom / Right Border都是0。“Blanking”是一行的同步时间,“Blanking”时间加上Active”Video时间就是一行的时间。“Blanking”又分为“Front Porch”、“Sync”、“Back Porch”三段。

行同步时序

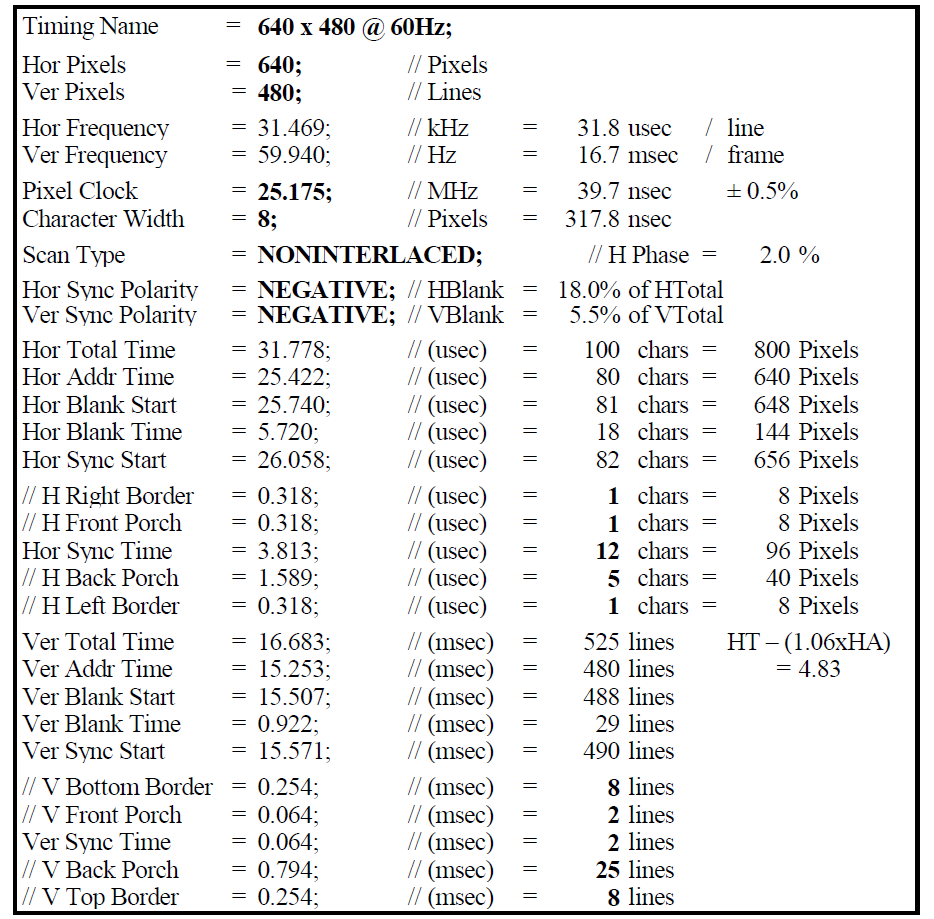

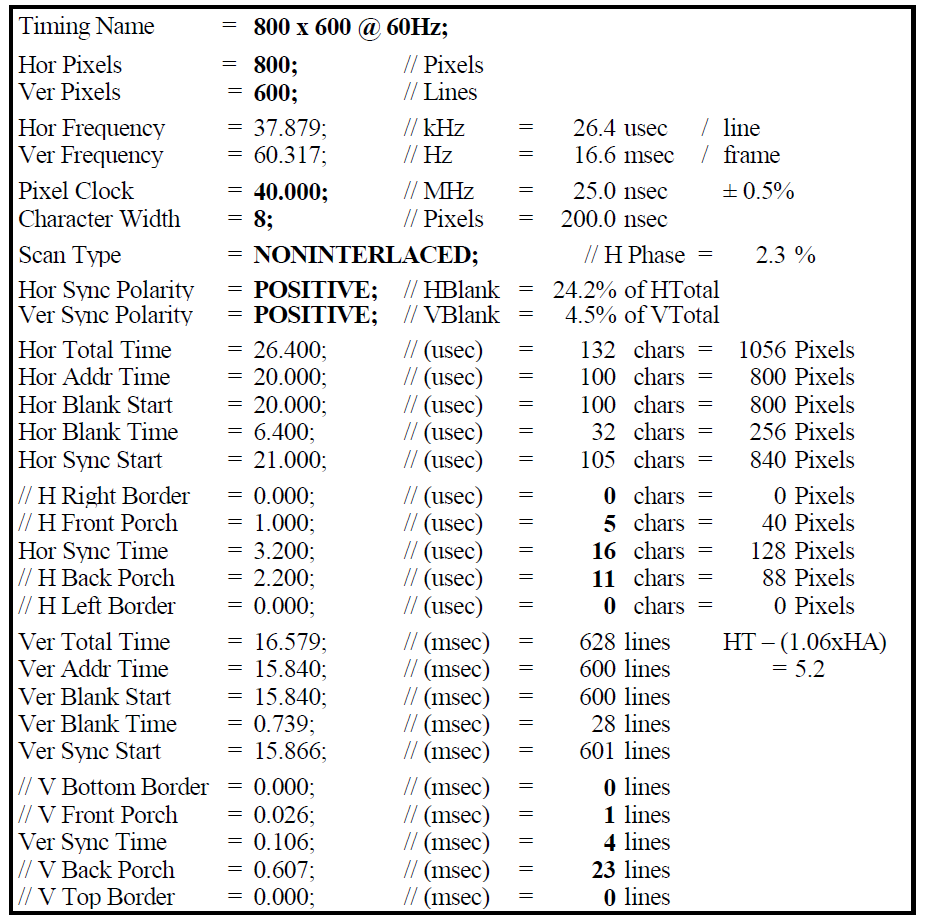

常见分辨率时序

640x480@60Hz时序参数

800x600@60Hz时序参数

1024x768@60Hz时序参数

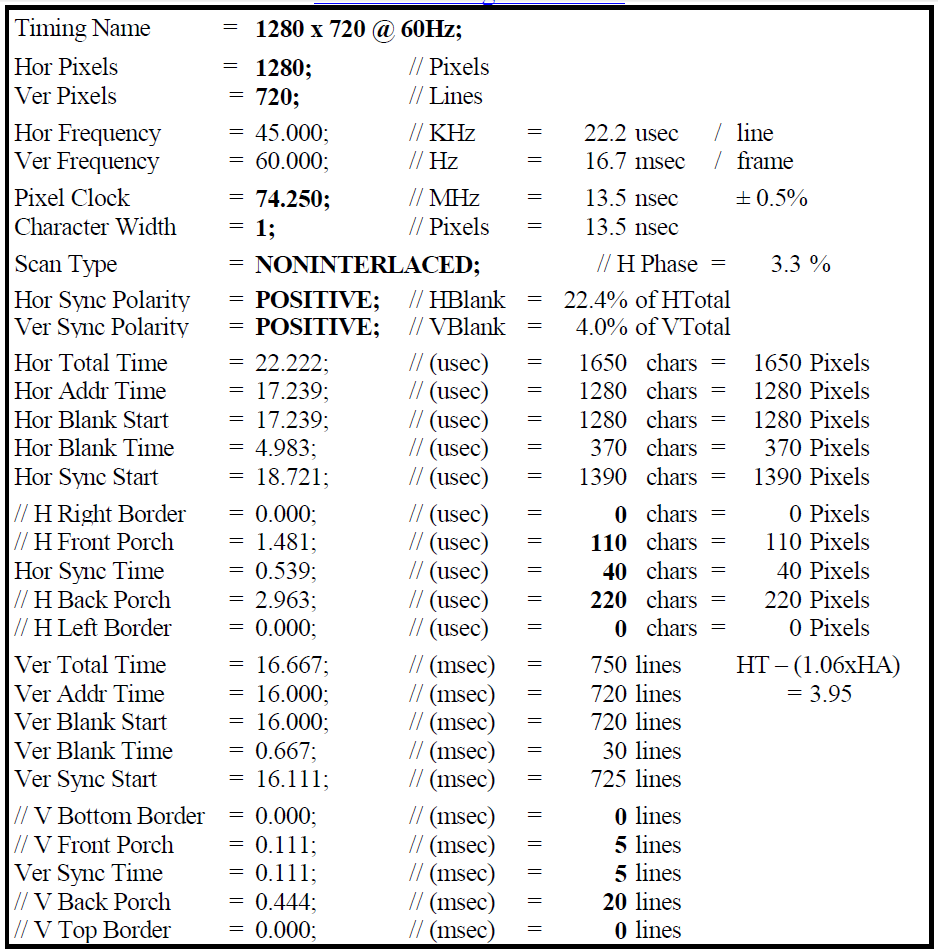

1280x720@60Hz时序参数

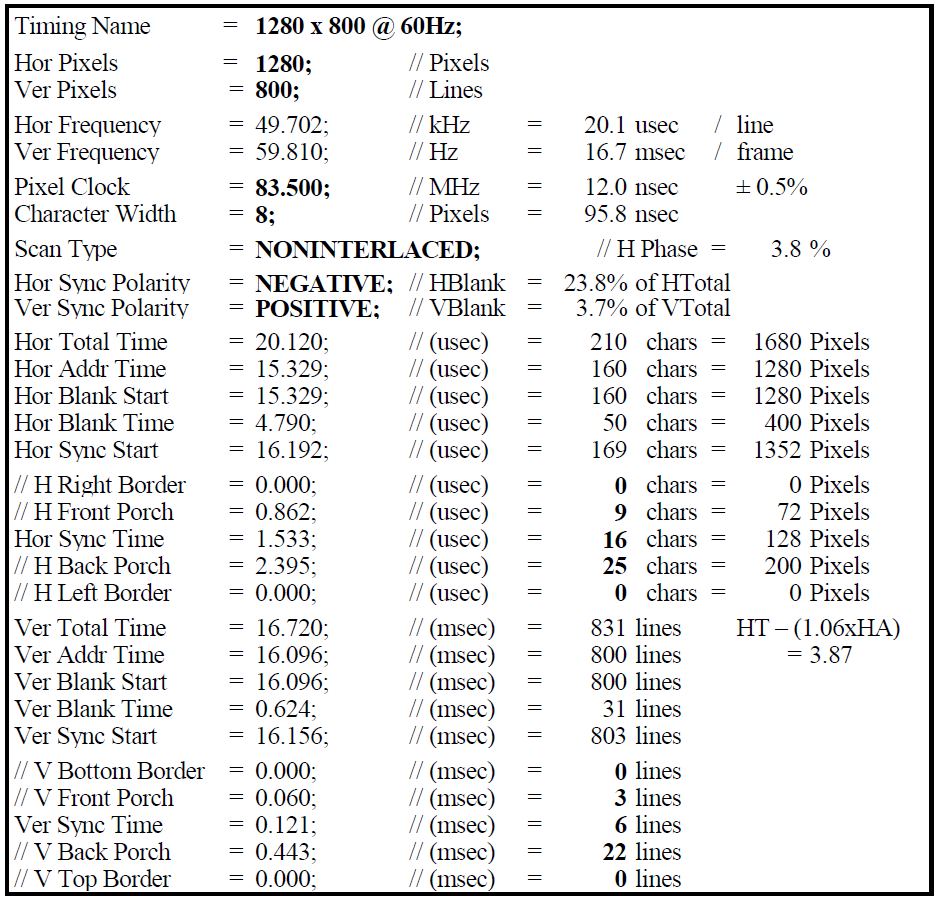

1280x800@60Hz时序参数

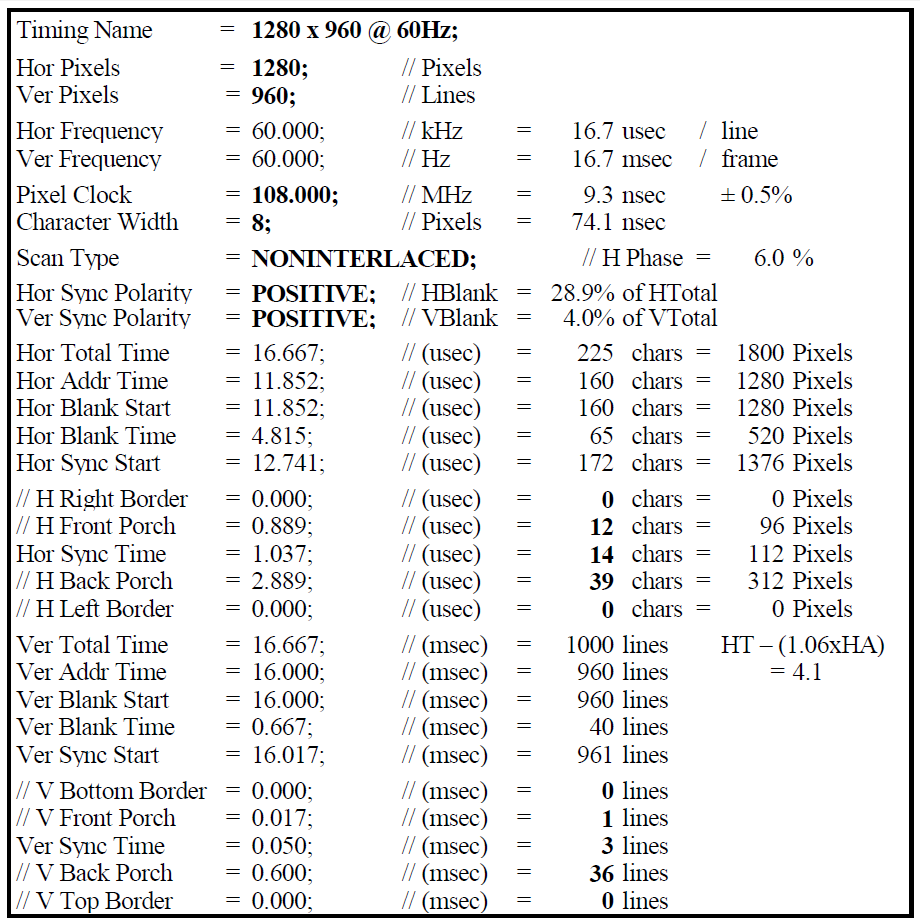

1280x960@60Hz时序参数

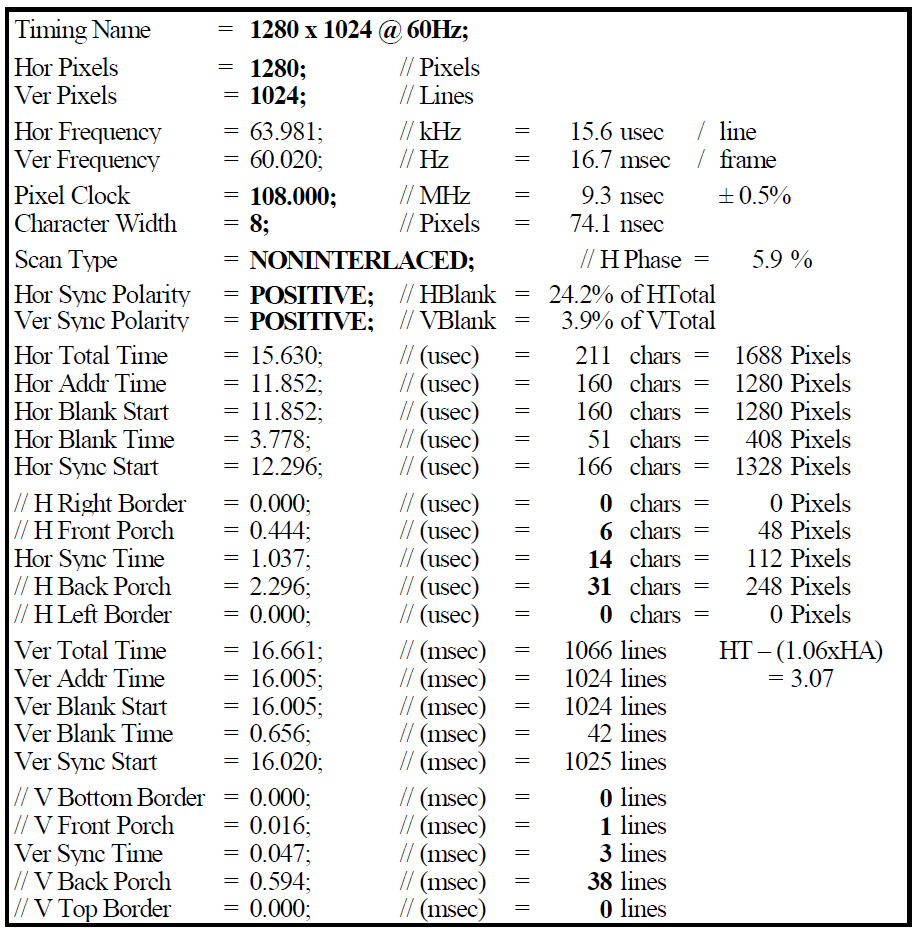

1280x1024@60Hz时序参数

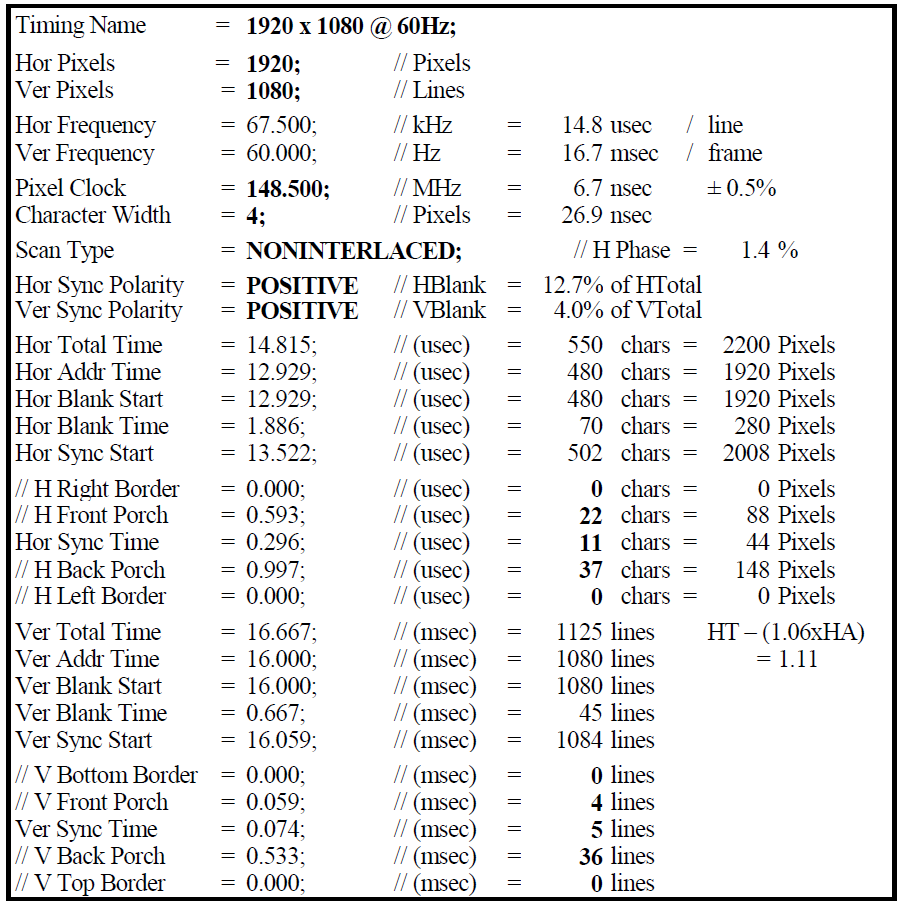

1920x1080@60Hz时序参数

3. HDMI输出程序设计

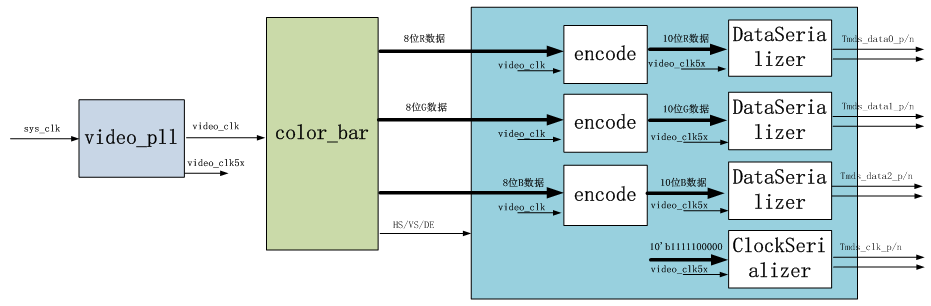

本实验将实现HDMI输出显示,verilog实现编程驱动HDMI输出,在HDMI显示器里显示测试图像彩条。HDMI输出显示模块分成3个模块实现,分别是时钟模块vidio_pll, 彩条生成模块color_bar和VGA转DVI模块dvi_encoder。实现的逻辑框图如下:

1. 彩条产生模块color_bar.v

color_bar.v是产生8种颜色的VGA格式的彩条,彩条分别为白、黄、青、绿、紫、红、蓝和黑。针对VGA的时序,行同步和场同步各使用一个计数器,行同步计数器用于产生行同步,行有效像素,场同步计数器用于产生场同步,场有效像素。同时根据计数器的值可以产生水平(X)和垂直(Y)坐标,通过坐标信息,可以实时显示一些图形。程序中预设了几种分辨率的时序参数,包括2款LCD液晶屏的,为后续的LCD验证试验做准备。

2. VGA转DVI模块dvi_encoder

dvi_encoder模块中包含两个模块encode和serdes_4b_10to1模块,实现RGB格式的图像转化成TMDS差分输出,来驱动HDMI显示。

1). encode: 红,绿,蓝的8位视频数据及时钟编码成10位的TMDS视频数据。关于编码的原因和方法我们已经在前面介绍过,具体如何实现,有兴趣的同学可以参考文档"08_其它学习资料\TMDS视频数据编码.doc"

2). serdes_4b_10to1:方法是通过两个OSERDESE2的串联把10比特的并行数据转换成串行发送出去。

4. HMDI输出试验现象

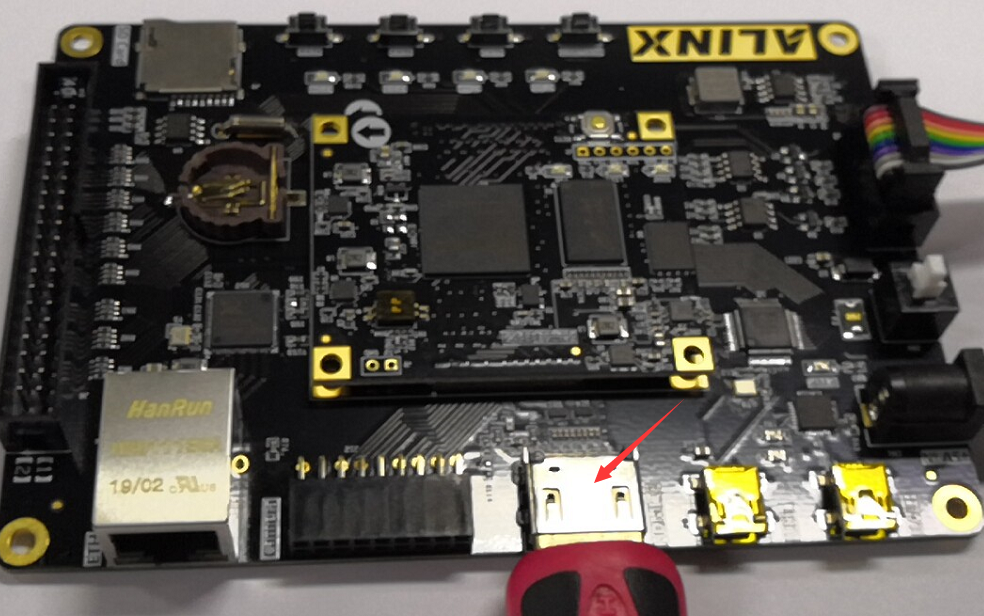

连接好开发板和显示器,需要注意,开发板的各个连接器不要带电热插拔,下载好试验程序,可以看到显示器显示8条彩条。开发板做为HDMI输出设备,只能通过HDMI显示设备来显示,不要试图通过笔记本电脑的HDMI接口来显示,因为笔记本的HDMI接口也是输出设备。

HDMI显示器连接

彩条显示

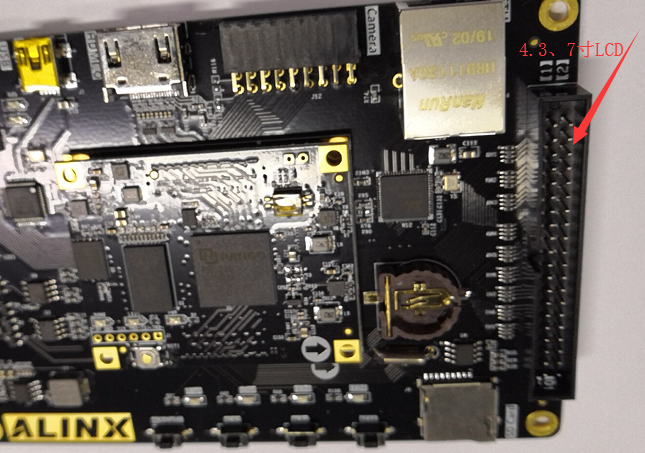

在用开发板做4.3寸LCD、7寸LCD屏显示实验时,LCD模块接开发板的J8扩展口,注意管脚不要接错。

如下图所示:

开发板与LCD屏连接